728x90

9.6 주소의 번역

- 주소 번역은 N원소 가상주소 공간(Virtual Address Space : VAS)과 M - 원소 물리주소 공간(Physical Address Space : PAS)의 원소들 간의 매핑이다.

- MAP : VAS → PAS U Ø

- MAP(A)

- A’ : 가상 주소 A의 데이터가 PAS의 물리주소 A’에 존재한다면

- Ø : 가상 주소 A의 데이터가 PAS의 물리메모리에 존재하지 않다면

- CPU내에 있는 제어 레지스터인 페이지 테이블 베이스 레지스터(Page table base register : PTBR)는 현재 페이지테이블을 가리킨다. n 비트 가상주소는 두 개의 컴포넌트를 가진다.

- p비트 가상페이지 오프셋(virtual page offset : VPO)과 (n-p) 비트 가상페이지 번호(virtual page number : VPN). MMU는 VPN을 사용해서 적합한 PTE를 선택한다. VPN0은 PTE0을 선택하고, VPN1은 PTE1을 선택하는식으로 진행된다. 대응되는 물리주소는 페이지테이블 엔트리에서 가져온 물리페이지 번호(Physical page number : PPN)와 가상주소에서 온 VPO를 연결한 것이다. 물리와 가상페이지가 모두 P바이트 이므로 물리페이지 오프셋 (Physical page offset : PPO)는 VPO랑 동일하다.

- 프로세서는 가상주소를 생성한다.

- MMU는 PTE 주소를 생성하고, 이것을 캐시/메인 메모리에 요청한다.

- 캐시/메인 메모리는 PTE를 MMU로 리턴한다.

- MMU는 물리주소를 구성하고 이것을 캐시/메인 메모리로 보낸다

- 캐시/메인 메모리는 요청한 데이트 워드를 프로세서로 보낸다.

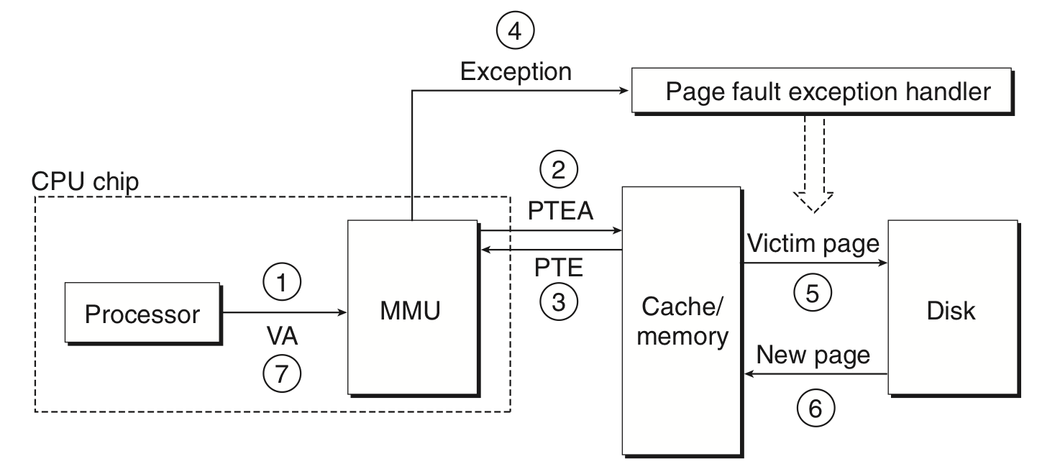

- 하드웨어가 모두 처리하는 페이지 적중과 달리, 페이지 오류를 처리하는 것은 하드웨어와 운영체제 커널과의 협력을 필요로 한다.

- 위 1 - 3 단계와 동일

- PTE의 유효비트는 0이므로 MMU는 예외를 발생시키고, CPU 내의 제어를 운영체제 커널의 페이지 오류 예외 핸들러로 이동시킨다.

- 오류 핸들러는 물리 메모리 내의 희생자 페이지를 결정하고, 만일 이 페이지가 수정되었다면 디스크로 페이지를 이동한다.

- 오류 핸들러는 새 페이지를 페이지 이동해서 들여오고, 메모리 내의 PTE를 갱신한다.

- 오류 핸들러는 처음의 프로세스로 돌아가고, 오류 인스트럭션은 재시작 된다. CPU는 문제를 일으킨 가상주소를 MMU로 다시 전송한다. 이 가상페이지는 이제 물리메모리내에 캐시되어 있으므로 적중이 발생하고 MMU가 단계를 수행한 후에 메인 메모리는 요청한 워드를 프로세서로 넘겨준다.

9.6.1 캐시와 VM의 통합

- 대부분의 시스템은 물리주소 지정을 선택한다. 물리주소를 사용하면, 다중 프로세스들이 캐시에서 블록을 갖는 것과 마찬가지로 가상페이지로 부터 블록을 공유하는 것이 단순해진다. 게다가 캐시는 보호 이슈를 다룰 필요가 없어지는데, 접근 권한이 주소 번역 과정의 일부로 체크되기 때문이다.

- 메인 아이디어는 주소번역이 캐시참조 이전에 일어난다는 점이다. 페이지 테이블 엔트리들이 다른 데이터 워드와 마찬가지로 캐싱될 수 있다는점에 주목해야 한다.

9.6.2 TLB를 사용한 주소 번역속도의 개선

- CPU가 가상주소를 생성할 때마다 MMU는 가상주소를 물리주소로 번역하기 위해 PTE를 참조 해야한다. 최악의 경우, 이것은 메모리로 부터 추가적인 선입 작업을 필요로 하며, 이를 위해서 수십에서 수백 사이클의 비용이 들게 된다. 만일 PTE가 L1에 캐싱되어 있다면, 이 비용은 2에서 1사이클로 줄어든다. 그렇지만, 많은 시스템들은 이 비용마저도 MMU내에 번역참조버퍼(Translation lookaside buffer : TLB)라고 부르는 작은 캐시를 포함해서 제거하려고 한다.

- TLB는 작은 가상주소 지정 캐시로, 각 라인은 하나의 PTE로 구성된 하나의 블록을 저장한다. TLB는 대개 높은 수준의 결합성을 가진다. 집합선택과 라인매칭을 위해 사용되는 index와 tag필드는 가상주소내의 가상페이지 번호에서 추출된다. 만일 TLB가 T = 2^t개의 집합을 가지면, TLB인덱스(TLBI)는 VPN의 t개의 최소 중요 비트와 나머지 비트들로 구성된 TLBtag(TLBT)로 이루어진다.

- TLB 적중이 발생할 때(대부분의 경우) 관련된 단계들을 보여준다. 핵심은 모든 주소번역 단계들이 온칩 on-chip MMU내에서 수행되기 때문에 매우 빠르다는 것이다.

- CPU는 가상주소를 생성한다.

- 2-3 MMU는 적당한 PTE를 TLB로부터 선입한다.

- MMU는 가상주소를 물리주소로 번역하고, 그것을 캐시/메인 메모리로 전송한다.

- 캐시/메인 메모리는 요청한 데이터 워드를 CPU로 리턴한다.

- TLB미스가 발생하면 MMU는 PTE를 L1캐시에서 선입해야한다. 새롭게 선입한 PTE는 TLB에 저장되며 기존 엔트리를 지울 수도 있다.

9.6.3 다중 레벨 페이지 테이블

- 지금까지 시스템이 주소를 번역하기 위해 한 개의 페이지 테이블을 사용한다고 가정해왔다. 그러나 만일 32비트 주소공간, 4KB 페이지, 4바이트 PTE인 경우 응용이 작은 크기의 가상주소 공간만 참조하는 경우에도 메모리에 항상 4MB 페이지 테이블을 필요로 하게 된다. 이 문제는 64비트 주소공간을 사용하는 시스템에 대해서 더 악화된다.

- 페이지 테이블을 압축하는 보편적인 접근법은 대신 페이지 테이블의 계층구조를 사용하는 것이다. 4바이트 페이지 테이블 엔트리를 갖는 4KB로 나누어진 32비트 가상주소 공간이 다음과 같은 형태를 갖는다고 가정하자.

- 첫 번째 2K 메모리 페이지는 코드와 데이터에 할당되고, 다음 6K 페이지는 미할당 상태이며, 다음 1023개의 페이지들 또한 미 할당 상태, 다음 페이지는 사용자 스택에 할당되었다.

- 1단계 테이블의 각 PTE는 4M의 가상주소 공간 크기를 매핑하는 역할을 하며, 이들 각각의 블록은 1,024개의 연속적인 페이지들로 이루어진다. 예를 들어, PTE0은 첫 번째 블록을, PTE1은 다음 블록식으로 계속 진행된다. 주소공간이 4GB라면 1,024PTE는 전체 공간을 커버하는데 충분하다.

- 만일 블록 i안의 모든 페이지들이 할당된다면 1단계 PTE i는 널이다. 예를 들어 위 그림에서 블록 2 - 7은 미할당 상태다. 그렇지만, 최소한 블록 i의 한 개 페이지가 할당된다면, 1단계 PTE i는 2단계 페이지테이블의 베이스를 가리킨다.

- 2단계 페이지테이블 내의 각 PTE들은 4KB 가상메모리 페이지를 관리하며, 이것은 앞에서 단일 레벨 페이지 테이블과 동일하다. 4바이트 PTE인 경우 각각 1단계와 2단계 페이지테이블은 4KB이고, 이들은 편리하게도 페이지와 같은 크기다.

- 이 기법은 메모리 요구량을 두 가지 방법으로 줄여준다.

- 첫째는 만일 1단계 테이블의 PTE가 널이면, 해당 2단계 페이지가 존재 할 필요가 없어진다. 이것은 상당한 잠재적인 절약을 의미하는데, 그것은 전형적인 프로그램에 대한 대부분의 4GB 가상주소 공간이 미할당 상태기 때문이다.

- 둘째는 1단계 테이블만이 항상 메인 메모리에 있을 필요가 있다는 것이다. 2단계 페이지 테이블은 이들이 필요할 때 VM시스템에 의해서 생성되고, 페이지 인 또는 아웃될 수 있으며, 이로 인해 메인 메모리로의 압박을 줄일 수 있다. 과도하게 사용된 2단계 페이지 테이블만이 메인메모리에 캐시 될 필요가 있다.

- K단계 페이지 테이블 계층 구조로 주소를 번역하는 과정

- 가상주소는 K개의 VPN 하나의 VPO로 나누어진다. 각각의 VPN i 1≤ i≤k 는 레벨 i에서 페이지테이블의 인덱스이다. 레벨 j 테이블에서 각각의 PTE는 1≤j≤k-1, 레벨 j+1에 있는 일부 페이지 테이블의 베이스를 가리킨다. 레벨 k 테이블에 있는 각각의 PTE는 일부 물리페이지의 PPN또는 디스크 블록의 주소를 포함한다. 물리주소를 구성하기 위해서 MMU는 PPN을 결정하기 전에 kPTE틀에 접근해야한다. 단일 레벨 계층구조처럼 PPO,VPO는 동일하다

- k개의 PTE에 접근하는 것은 언뜻 보기에 비실용적이고 값비싼것 처럼 보일지도 모른다. 그렇지만 다른 레벨의 페이지테이블에서 PTE를 캐싱하는 방법으로 여기서 TLB가 구출된다. 실제로 멀티 레벨 페이지 테이블로 주소를 번역하는 것은 단일 레벨 페이지 테이블로 하는것에 비해 많이 느려지는 것은 아니다.

728x90

'책 > CSAPP' 카테고리의 다른 글

| CSAPP 9.9.4 - 9.9.7 (2) | 2024.01.31 |

|---|---|

| CSAPP 9.8 - 9.9.3 (0) | 2024.01.30 |

| CSAPP 9-9.5 (1) | 2024.01.28 |

| CSAPP 3.11 (1) | 2024.01.27 |

| CSAPP 3.10.3 - 3.10.5 (1) | 2024.01.26 |